# Bandgap Extraction at 10 K to Enable Leakage Control in Carbon Nanotube MOSFETs

Qing Lin<sup>®</sup>, *Graduate Student Member, IEEE*, Gregory Pitner<sup>®</sup>, *Member, IEEE*, Carlo Gilardi<sup>®</sup>, *Graduate Student Member, IEEE*, Sheng-Kai Su, Zichen Zhang, Edward Chen, Prabhakar Bandaru, *Member, IEEE*, Andrew Kummel, *Member, IEEE*, Han Wang, Matthias Passlack<sup>®</sup>, *Fellow, IEEE*, Subhasish Mitra<sup>®</sup>, *Fellow, IEEE*, and H.-S. Philip Wong<sup>®</sup>, *Fellow, IEEE*

Abstract—Carbon nanotube (CNT) transistors exemplify the fundamental tradeoff between desirable high mobility and undesirable leakage current due to the small effective mass and bandgap. To understand leakage current limits in high-speed CNT transistors, electrical bandgaps are extracted on 12 single-CNT top-gate MOSFETs from the energy gap between thermionic emission and band-to-band tunneling (BTBT) at 10 K. At 300 K the minimum I<sub>OFF</sub> at 0.5 V V<sub>DS</sub> is analyzed as a function of bandgap between 0.96 eV and 0.43 eV with IOFF-MIN from 0.2 pA/CNT to 15 nA/CNT. NEGF simulation validates the bandgap extraction methodology and reproduces the experimental MOSFET IOFF-MIN data. A TCAD model calibrated to this work's leakage data projects the accessible I<sub>ON</sub>-I<sub>OFF</sub> design space bounded by CNT bandgap, indicating E<sub>G</sub> > 0.65 eV (d<sub>CNT</sub> < 1.3 nm) is needed to achieve 100 nA/ $\mu$ m at 0.5 V V<sub>DD</sub> and 250 CNT/ $\mu$ m for channel length above 20 nm. An  $E_G$  of 1.06 eV ( $d_{CNT}$  = 0.8 nm) can deliver 2750× tunable range of I<sub>OFF</sub> by adjusting V<sub>T</sub>, which exceeds the  $400 \times$  tunable range of I<sub>OFF</sub> used in Si CMOS platform technologies.

*Index Terms*— Carbon nanotube, CMOS, MOSFET, leakage current, band-to-band tunneling, bandgap extraction.

#### I. INTRODUCTION

**U**OW-DIMENSIONAL semiconductor channel materials such as Carbon Nanotube (CNT) are potentially advan-

Manuscript received November 11, 2021; revised December 18, 2021; accepted January 2, 2022. Date of publication January 7, 2022; date of current version February 24, 2022. This work was supported in part by the National Nanotechnology Coordinated Infrastructure (NNCI) under Grant ECCS-1542152 and Grant ECCS-1542148 and in part by member companies of the Stanford SystemX Alliance. The work of Qing Lin was supported in part by the Defense Advanced Research Projects Agency (DARPA) 3 Dimensional Monolithic System on a Chip (3DSoC) Program. The review of this letter was arranged by Editor D. Shahrjerdi. (*Qing Lin and Gregory Pitner contributed equally to this work.*) (*Corresponding authors: Qing Lin; Gregory Pitner.*)

Qing Lin, Carlo Gilardi, and Subhasish Mitra are with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: qinglin@stanford.edu).

Gregory Pitner, Han Wang, and Matthias Passlack are with Corporate Research, Taiwan Semiconductor Manufacturing Company, San Jose, CA 95134 USA (e-mail: gpitner@tsmc.com).

Sheng-Kai Su and Edward Chen are with Corporate Research, Taiwan Semiconductor Manufacturing Company, Hsinchu 30078, Taiwan.

Zichen Zhang, Prabhakar Bandaru, and Andrew Kummel are with the Department of Electrical Engineering, University of California at San Diego, San Diego, CA 92093 USA.

H.-S. Philip Wong is with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA, and also with Corporate Research, Taiwan Semiconductor Manufacturing Company, San Jose, CA 95134 USA.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2022.3141692.

Digital Object Identifier 10.1109/LED.2022.3141692

tageous for CMOS logic beyond the 2 nm technology node. Recent advances have demonstrated essential transistor components such as 6.5 k $\Omega$ /CNT contact resistance at a 10 nm contact length [1], dense CNT assembly up to 250 CNT/ $\mu$ m [2], and short-channel effect immunity down to 15 nm gate length [3]. However, the dependence of leakage current on CNT bandgap has not been investigated by experiment. This work aims to (1) introduce a new method to extract the CNT bandgap based on electrical characterization of top-gate MOSFET structures at 10 K, (2) measure the limits of the leakage current for a large range of bandgaps in single-CNT MOSFETs, and (3) calibrate a TCAD CNT device model to project the range of tunable off-current between the limits of high-performance off-current density ( $\sim 100 \text{ nA}/\mu \text{m}$ ) and band-to-band tunneling (BTBT) onset, with a view to identifying the range of CNT bandgaps suitable for logic platform technologies.

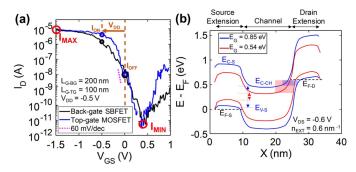

## II. UNDERSTANDING THE LEAKAGE CHALLENGE IN CARBON NANOTUBE TRANSISTORS

High-speed compute and low-energy system-on-chip applications utilize granular standard cell-level control over transistor leakage by selecting high threshold voltage (V<sub>TH</sub>) for non-critical path circuits, with selective use of low V<sub>TH</sub> to meet timing requirements on critical paths. In Fig. 1(a) the I<sub>D</sub>-V<sub>GS</sub> for a typical CNT Schottky-barrier FET (SBFET) and CNT MOSFET are displayed, labeling: (1) I<sub>OFF</sub> at V<sub>GS</sub> = 0, (2) I<sub>ON</sub> at V<sub>GS</sub> = V<sub>DS</sub> = V<sub>DD</sub>, (3) I<sub>MAX</sub> at largest |V<sub>GS</sub>|, and (4) I<sub>MIN</sub> at smallest measured I<sub>D</sub>. I<sub>MIN</sub> is the point beyond which any increase in V<sub>TH</sub> does not reduce leakage current, and therefore is the key metric to evaluate the limits of energy-efficiency.

While previous literature [4]–[6] study mostly SBFET with gate overlapping source and drain contacts or asymmetric-SBFET with gate overlapping the source only, this work focuses on CNT MOSFET with doped source and drain extension region. Comparing MOSFET and SBFET, a MOSFET has (1) steeper above-V<sub>TH</sub> transition to on-state which enables higher current at the same  $V_{DD}$  and  $I_{OFF}$ , (2) lower parasitic capacitance between the gate and contacts which enables faster switching, and (3) the band-to-band tunneling (BTBT) leakage mechanism that influences I<sub>MIN</sub> in MOSFET is distinct from the ambipolar leakage mechanism which determines I<sub>MIN</sub> in SBFETs, so should be considered separately. Fig. 1(b) explains the how BTBT (and thus  $I_{MIN}$ ) is strongly influenced by channel material bandgap ( $E_{G}$ ), however the correlation between IOFF in CNT MOSFET and bandgap has not been previously reported [7]–[11].

0741-3106 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. (a) Example  $I_D$ -V<sub>GS</sub> for single-CNT SBFET (black) and MOSFET (blue) from same CNT channel before/after top gate deposition [2]. The x-axis has been shifted to set  $I_{OFF}$  of 10 nA in both devices. (b) Band diagrams generated by TCAD simulation illustrate CNT MOSFET leakage sensitivity to bandgap (E<sub>G</sub>). The vertical arrow on the source side indicates the energy transition required for source-to-channel BTBT. The highlighted region on the drain side indicates the energy range where BTBT may occur between the conduction band edge in channel (E<sub>C-CH</sub>) and unoccupied states below the fermi-level in the drain valence band (E<sub>F-D</sub>). At same bias conditions, smaller bandgap has larger BTBT due to both smaller source-to-channel energy transition and larger energy overlap between channel E<sub>C-CH</sub> and drain E<sub>F-D</sub>.

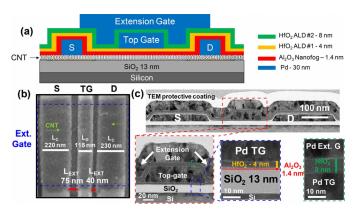

Fig. 2. Dual top-gate MOSFET device structure. (a) Cross-section schematic, (b) top-down scanning electron micrograph and (c) cross-section transmission electron micrograph of a typical device after fabrication. The 1.4 nm  $Al_2O_3$  film is an interfacial oxide deposited by nanofog method [3]. All devices in this work have the same dimensions.

#### **III. CNT MOSFET BANDGAP EXTRACTION**

MOSFETs with single-CNT channels are fabricated on CVD-grown aligned CNTs with an intentionally broad diameter distribution ( $d_{CNT} \sim 1.3$  nm,  $\sigma_{CNT} \sim 0.4$  nm) [12]. A top-gate electrode modulates the channel potential, and an overlapping top-gate extension electrode is provided in this test structure to modulate the doping level in the extension (Fig. 2(a)). In a practical device technology, solid-state doping will be used instead of the extension gate [13]. Figs. 2(b,c) verify the device structure after fabrication and label all key dimensions.

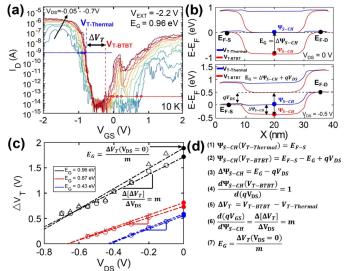

To better understand how BTBT depends on the bandgap, a novel bandgap extraction method is developed as follows:

- 1. Measure  $I_D$ -V<sub>GS</sub> at 10 K to clearly identify the onset of BTBT (Fig. 3(a)) by limiting the thermal tail. Repeat for multiple V<sub>DS</sub>.

- 2. Define thermal branch threshold (V<sub>T-Thermal</sub>) as device enters subthreshold region ( $I_D = 1$  nA) and the tunneling branch threshold ( $V_{T-BTBT}$ ) at onset of BTBT when  $I_D$  exceeds the noise level of 0.05 pA, corresponding to channel-source and channel-drain band alignments (Fig. 3(b)).

Fig. 3. (a) Bandgap extraction methodology begins with  $I_D$ -V<sub>GS</sub> at 10 K. (b) Band diagrams corresponding to V<sub>T-Thermal</sub> (blue) when device enters subthreshold region and V<sub>T-BTBT</sub> (red) at onset of BTBT for V<sub>DS</sub> of 0 V (top) and -0.5 V (bottom) for a E<sub>G</sub> = 0.85 eV. (c)  $_1$ V<sub>T</sub> versus V<sub>DS</sub> for multiple extension gate bias (V<sub>EXT</sub>) to extract gate efficiency *m*, from linear regression slope and *y*-intercept at V<sub>DS</sub> = 0. (d) Derivation of bandgap using parameters  $\Delta$ V<sub>T</sub>(V<sub>DS</sub> = 0) and *m* found in (c). This approach is only valid if extensions are degenerately doped.

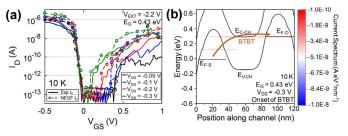

Fig. 4. (a) Comparison of NEGF-simulated and experimental I<sub>D</sub>-V<sub>GS</sub> for a CNT MOSFET of E<sub>G</sub> = 0.43 eV at 10 K, showing good agreement in the onset of BTBT. (b) Band profile and position-resolved current spectrum at the onset of BTBT for V<sub>DS</sub> = -0.3 V, showing main current contribution is BTBT while thermionic emission is negligible.

3. Fit  $\Delta V_T = V_{T-BTBT} - V_{T-Thermal}$  versus  $V_{DS}$  with a linear function (Fig. 3(c)). The y-intercept represents the gate voltage swing to shift the channel surface potential at the valence band ( $\Psi_{S-CH}$ ) exactly by  $E_G$  between these two thresholds at zero drain bias. The slope is the gate efficiency coefficient, which converts the gate voltage swing to channel surface-potential ( $\Psi_{S-CH}$ ) as derived in Fig. 3(d).

NEGF modeling is used to validate the bandgap extraction method based on the same dual top gate structure. The simulation includes inelastic BTBT mediated by optical phonons [14], [15]. Due to computing limitations, a shorter gate length of 40 nm is used where direct source-to-drain tunneling remains negligible and the extracted bandgap is used as the input. Fig. 4(a) compares the experimental (solid lines) and NEGF-simulated  $I_D$ -V<sub>GS</sub> curve (dashed lines) at 10 K, showing good agreement in V<sub>T-BTBT</sub> at the onset of BTBT. The bandgap extraction method is repeated on the NEGF-generated  $I_D$ -V<sub>GS</sub> curves at 10 K and results in the same bandgap, further confirming the validity of this approach. The band diagram and current spectrum in Fig. 4(b) highlight the conduction path for phonon-assisted BTBT where carriers injected at the source

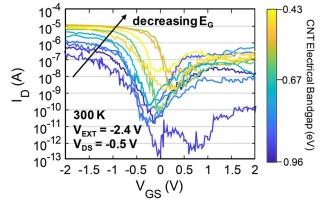

Fig. 5.  $I_D\text{-}V_{GS}$  at 300 K for 12 CNFETs with  $E_G$  = from 0.96 eV to 0.43 eV at -0.5V  $V_{DS}.$

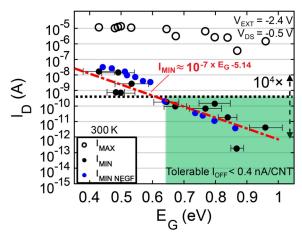

Fig. 6. Experimental I<sub>MIN</sub> and I<sub>MAX</sub> at 300 K versus E<sub>G</sub> extracted for 12 single-CNT top-gate MOSFETs for V<sub>DS</sub> = -0.5 V, showing good agreement with NEGF-simulated I<sub>MIN</sub>. The I<sub>MIN</sub> increases by ~4 order of magnitude, while I<sub>MAX</sub> only increases about 1 order of magnitude as E<sub>G</sub> decreases from 0.96 eV to 0.43 eV. Large bandgap CNFETs have clearly demonstrated sub-10 pA/CNT 0.5V V<sub>DS</sub>. Error bars indicate the uncertainty in the extracted bandgap accounting for the margin of error in the fitted slope, y-intercept, as well as the averaging effect from 3-5 repeated measurements.

can inelastically tunnel to the bounded states in the channel before tunneling to the drain.

# IV. CNT MOSFET LEAKAGE ANALYSIS AND TCAD PERFORMANCE PROJECTION

Fig. 5 shows the  $I_D$ -V<sub>GS</sub> of 12 single-CNT MOSFETs. The extracted bandgaps range from 0.43 ± 0.05 eV to 0.96 eV ± 0.05 eV, which explain the significant difference in  $I_{MIN}$  at constant V<sub>DS</sub>. Fig. 6 shows experimental  $I_{MIN}$  increases from sub-1 pA/CNT to more than 10 nA/CNT as E<sub>G</sub> decreases from 0.96 eV to 0.43 eV at V<sub>DS</sub> = -0.5 V at 300 K, with a good agreement from NEGF-simulated  $I_{MIN}$ . The CNT bandgap is inversely proportional to CNT diameter from band structure theory with tight-binding approximation and the diameter is determined by the (n, m) chirality of CNT [16]. Therefore, this data may guide future effort to control  $I_{MIN}$  and  $I_{OFF}$  variation through chirality and diameter selection [17].

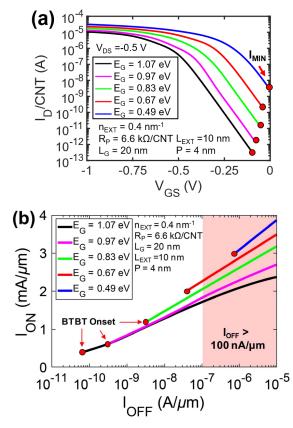

The I<sub>MIN</sub> data in previous section enables accurate TCADprojected leakage behaviors for CNT MOSFETs. The TCAD model is calibrated with contact resistance, CNT density, and electrostatics that were experimentally demonstrated in the literature [1]–[3] and the I<sub>MIN</sub> in this work. Fig. 7(a) shows the I<sub>D</sub>-V<sub>GS</sub> for 5 different bandgaps where the I<sub>MIN</sub> is calculated

Fig. 7. (a) I<sub>D</sub>-V<sub>GS</sub> of CNFETs for 5 CNT bandgaps based on the TCAD model calibrated to this work's experimental I<sub>MIN</sub> data, contact resistance R<sub>P</sub> = 6.6 kΩ/CNT per contact [1], CNT density 250 CNTs/µm (pitch = 4 nm) [2], gate oxide capacitance from ref. [3], and moderate extension doping of 0.4 holes/nm. (b) TCAD projection of I<sub>ON</sub>/µm versus I<sub>OFF</sub>. Each curve represents accessible on/off current on the I<sub>D</sub>-V<sub>GS</sub> curve by V<sub>TH</sub> shift with a window size V<sub>GS</sub> = V<sub>DS</sub> = V<sub>DD</sub> for V<sub>DD</sub> of 0.5 V.

based on the trendline in Fig. 6, fitted on the experimental data. Fig. 7(b) highlights the accessible off-current and oncurrent density between the lowest  $I_{OFF}$  limited by BTBT and a high-performance off-current specification of 100 nA/ $\mu$ m for a range of bandgaps at 0.5 V V<sub>DD</sub>. The key new insights are (1) due to BTBT a very small design space exists for  $E_G \sim 0.67$  eV (d  $\sim 1.27$  nm), and CNT with even smaller bandgaps (larger diameter) have no design space at all at 0.5 V V<sub>DD</sub>; (2)  $E_G \sim 0.83$  eV or larger (d<sub>CNT</sub>  $\sim 1$  nm or smaller) tradeoff a linear decrease in  $I_{ON}$  with exponential improvement in device leakage, and (3) an  $E_G$  of 0.97 eV (d<sub>CNT</sub>  $\sim 0.88$  nm) can achieve 330× range of accessible  $I_{OFF}$  which is comparable to Si CMOS platform technology [18].

### V. CONCLUSION

In summary, a new methodology is developed to extract the CNT bandgaps in CNT MOSFETs based on electrical characterizations at 10 K. With this method, the CNT MOSFET leakage current is reported across a range of bandgap for the first time. NEGF simulation validates the bandgap extraction method and leakage current dependence on bandgap. This work also projects the on- and off-current achievable between limits of BTBT-onset and high leakage power. Future studies should investigate additional leakage from source-to-drain tunneling (SDT) below 20 nm  $L_G$  and utilize solid-state doping methods in the extension region.

#### REFERENCES

- [1] G. Pitner, G. Hills, J. P. Llinas, K.-M. Persson, R. Park, J. Bokor, S. Mitra, and H.-S.-P. Wong, "Low-temperature side contact to carbon nanotube transistors: Resistance distributions down to 10 nm contact length," *Nano Lett.*, vol. 19, no. 2, pp. 1083–1089, Jan. 2019, doi: 10.1021/acs.nanolett.8b04370.

- [2] L. Liu, J. Han, L. Xu, J. Zhou, C. Zhao, S. Ding, H. Shi, M. Xiao, L. Ding, Z. Ma, C. Jin, Z. Zhang, and L.-M. Peng, "Aligned, highdensity semiconducting carbon nanotube arrays for high-performance electronics," *Science*, vol. 368, no. 6493, pp. 850–856, May 2020, doi: 10.1126/science.aba5980.

- [3] G. Pitner, Z. Zhang, Q. Lin, S.-K. Su, C. Gilardi, C. Kuo, H. Kashyap, T. Weiss, Z. Yu, T.-A. Chao, L.-J. Li, S. Mitra, H.-S.-P. Wong, J. Cai, A. Kummel, P. Bandaru, and M. Passlack, "Sub-0.5 nm interfacial dielectric enables superior electrostatics: 65 mV/dec topgated carbon nanotube FETs at 15 nm gate length," in *IEDM Tech. Dig.*, Dec. 2020, pp. 3.5.1–3.5.4, doi: 10.1109/IEDM13553.2020. 9371899.

- [4] C. Zhao, D. Zhong, L. Liu, Y. Yang, H. Shi, L.-M. Peng, and Z. Zhang, "Strengthened complementary metal–oxide–semiconductor logic for small-band-gap semiconductor-based high-performance and low-power application," ACS Nano, vol. 14, no. 11, pp. 15267–15275, Oct. 2020, doi: 10.1021/acsnano.0c05554.

- [5] T. Srimani, G. Hills, X. Zhao, D. Antoniadis, J. A. del Alamo, and M. M. Shulaker, "Asymmetric gating for reducing leakage current in carbon nanotube field-effect transistors," *Appl. Phys. Lett.*, vol. 115, no. 6, Aug. 2019, Art. no. 063107, doi: 10.1063/1.5098322.

- [6] A. Javey, R. Tu, D. B. Farmer, J. Guo, R. G. Gordon, and H. Dai, "High performance n-type carbon nanotube field-effect transistors with chemically doped contacts," *Nano Lett.*, vol. 5, no. 2, pp. 345–348, Feb. 2005, doi: 10.1021/nl047931j.

- [7] C.-S. Pang, S.-J. Han, and Z. Chen, "Steep slope carbon nanotube tunneling field-effect transistor," *Carbon*, vol. 180, pp. 237–243, Aug. 2021, doi: 10.1016/j.carbon.2021.03.068.

- [8] G. Zeevi, A. Razin, and Y. E. Yaish, "PN junction and band to band tunneling in carbon nanotube transistors at room temperature," *Nanotechnology*, vol. 32, no. 33, May 2021, Art. no. 335202, doi: 10.1088/1361-6528/abfd56.

- [9] J. Appenzeller, Y.-M. Lin, J. Knoch, Z. Chen, and P. Avouris, "Comparing carbon nanotube transistors—The ideal choice: A novel tunneling device design," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2568–2576, Dec. 2005, doi: 10.1109/TED.2005. 859654.

- [10] J. Appenzeller, Y.-M. Lin, J. Knoch, and P. Avouris, "Band-toband tunneling in carbon nanotube field-effect transistors," *Phys. Rev. Lett.*, vol. 93, no. 19, Nov. 2004, Art. no. 196805, doi: 10.1103/ physrevlett.93.196805.

- [11] J. Chen, C. Klinke, A. Afzali, K. Chan, and P. Avouris, "Self-aligned carbon nanotube transistors with novel chemical doping," in *IEDM Tech. Dig.*, Dec. 2004, pp. 695–698, doi: 10.1109/IEDM.2004.1419264.

- [12] N. Patil, A. Lin, E. R. Myers, K. Ryu, A. Badmaev, C. Zhou, H.-S. P. Wong, and S. Mitra, "Wafer-scale growth and transfer of aligned single-walled carbon nanotubes," *IEEE Trans. Nanotechnol.*, vol. 8, no. 4, pp. 498–504, Jul. 2009, doi: 10.1109/TNANO.2009.2016562.

- [13] L. S. Liyanage, X. Xu, G. Pitner, Z. Bao, and H.-S.-P. Wong, "VLSIcompatible carbon nanotube doping technique with low work-function metal oxides," *Nano Lett.*, vol. 14, no. 4, pp. 1884–1890, Mar. 2014, doi: 10.1021/nl404654j.

- [14] S. O. Koswatta, S. Hasan, M. S. Lundstrom, M. P. Anantram, and D. E. Nikonov, "Nonequilibrium Green's function treatment of phonon scattering in carbon-nanotube transistors," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2339–2351, Sep. 2007, doi: 10.1109/TED.2007.902900.

- [15] (Oct. 2021). EOLAS Proprietary TCAD Tool Q. [Online]. Available: https://eolasdesigns.com

- [16] H. Ajiki and T. Ando, "Electronic states of carbon nanotubes," *J. Phys. Soc. Jpn.*, vol. 62, no. 4, pp. 1255–1266, Apr. 1993, doi: 10.1143/JPSJ.62.1255.

- [17] F. Yang, M. Wang, D. Zhang, J. Yang, M. Zheng, and Y. Li, "Chirality pure carbon nanotubes: Growth, sorting, and characterization," *Chem. Rev.*, vol. 120, no. 5, pp. 2693–2758, Feb. 2020, doi: 10.1021/acs.chemrev.9b00835.

- [18] G. Yeap, X. Chen, B. R. Yang, C. P. Lin, F. C. Yang, Y. K. Leung, D. W. Lin, C. P. Chen, K. F. Yu, D. H. Chen, C. Y. Chang, S. S. Lin, H. K. Chen, P. Hung, C. S. Hou, Y. K. Cheng, J. Chang, L. Yuan, C. K. Lin, C. C. Chen, Y. C. Yeo, M. H. Tsai, Y. M. Chen, H. T. Lin, C. O. Chui, K. B. Huang, W. Chang, H. J. Lin, K. W. Chen, R. Chen, S. H. Sun, Q. Fu, H. T. Yang, H. L. Shang, H. T. Chiang, C. C. Yeh, T. L. Lee, C. H. Wang, S. L. Shue, C. W. Wu, R. Lu, W. R. Lin, J. Wu, F. Lai, P. W. Wang, Y. H. Wu, B. Z. Tien, Y. C. Huang, L. C. Lu, J. He, Y. Ku, J. Lin, M. Cao, T. S. Chang, S. M. Jang, H. C. Lin, Y. C. Peng, J. Y. Sheu, and M. Wang, "5 nm CMOS production technology platform featuring full-fledged EUV, and high mobility channel FinFETs with densest 0.021  $\mu$ m<sup>2</sup> SRAM cells for mobile SoC and high performance computing applications," in IEDM Tech. Dig., 2019, Dec. pp. 36.7.1-36.7.4, doi: 10.1109/IEDM19573.2019.8993577.